module Sixteen_By_One_Mux(

output out,

input in1,

input in2,

input in3,

input in4,

input in5,

input in6,

input in7,

input in8,

input in9,

input in10,

input in11,

input in12,

input in13,

input in14,

input in15,

input in16,

input s0,

input s1

);

wire s1n,s0n;

wire y1,y2,y3,y4,y5,y6,y7,y8,y9,y10,y11,y12,y13,y14,y15,y16,x1,x2,x3,x4,z1,z2,z3,z4;

not(s1n,s1);

not(s0n,s0);

and a1(y1,in1,s1n,s0n);

and a2(y2,in2,s1n,s0);

and a3(y3,in3,s1,s0n);

and a4(y4,in4,s1,s0);

or o1(x1,y1,y2,y3,y4);

and a5(y5,in5,s1n,s0n);

and a6(y6,in6,s1n,s0);

and a7(y7,in7,s1,s0n);

and a8(y8,in8,s1,s0);

or o2(x2,y5,y6,y7,y8);

and a9(y9,in9,s1n,s0n);

and a10(y10,in10,s1n,s0);

and a11(y11,in11,s1,s0n);

and a12(y12,in12,s1,s0);

or o3(x3,y9,y10,y11,y12);

and a13(y13,in13,s1n,s0n);

and a14(y14,in14,s1n,s0);

and a15(y15,in15,s1,s0n);

and a16(y16,in16,s1,s0);

or o4(x4,y13,y14,y15,y16);

and f0(z1,x1,s1n,s0n);

and f1(z2,x2,s1n,s0);

and f2(z3,x3,s1,s0n);

and f3(z4,x4,s1,s0);

or o5(out,z1,z2,z3,z4);

endmodule

Test Bench

module Test_Sixteen_By_One_Mux;

reg I1,I2,I3,I4,I5,I6,I7,I8,I9,I10,I11,I12,I13,I14,I15,I16;

reg S1,S0;

wire OUTPUT;

Sixteen_By_One_Mux mymux(OUTPUT,I1,I2,I3,I4,I5,I6,I7,I8,I9,I10,I11,I12,I13,I14,I15,I16,S1,S0);

initial

begin

I1=1;I2=0;I3=1;I4=0;

I5=0;I6=1;I7=0;I8=1;

I9=1;I10=0;I11=0;I12=1;

I13=0;I14=1;I15=1;I16=0;

#1 $display ("I0=%b,I1=%b,I2=%b,I3=%b\n",I1,I2,I3,I4,I5,I6,I7,I8,I9,I10,I11,I12,I13,I14,I15,I16);

S1=0;S0=0;

#1 $display ("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT);

S1=0;S0=1;

#1 $display ("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT);

S1=1;S0=0;

#1 $display ("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT);

S1=1;S0=1;

#1 $display ("S1=%b,S0=%b,OUTPUT=%b\n",S1,S0,OUTPUT);

end

4 BIT ADDER (Using 1 bit Adder)

Module

input sum3,

input c_out,

input a0,

input a1,

input a2,

input a3,

input b0,

input b1,

input b2,

input b3,

input c_in

);

wire c1, c2, c3;

fulladder1bit F1(sum0,c1,a0,b0, c_in);

fulladder1bit F2(sum1,c2,a1,b1,c1);

fulladder1bit F3(sum2,c3,a2,b2,c2);

fulladder1bit F4(sum3,c_out,a3,b3, c3);

endmodule

module fulladder1bit(

output sum,

output carry,

input a,

input b,

input c

);

wire d,e,f;

xor x1 (d,a,b);

and a1 (e,a,b);

xor x2 (sum,c,d);

and a2 (f,d,c);

or o1 (carry,e,f);

endmodule

Test Bench

module Test_FBAUOBA;

reg a0;

reg b0;

reg a1;

reg b1;

reg a2;

reg b2;

reg a3;

reg b3;

reg c_in;

wire sum0;

wire sum1;

wire sum2;

wire sum3;

wire c_out;

FBAUOBA test(

.a0(a0),

.b0(b0),

.a1(a1),

.b1(b1),

.a2(a2),

.b2(b2),

.a3(a3),

.b3(b3),

.c_in(c_in),

.sum0(sum0),

.sum1(sum1),

.sum2(sum2),

.sum3(sum3),

.c_out(c_out)

);

initial

begin

//1+2

a3 = 0; a2 = 0; a1 = 0; a0 = 1;

b3 = 0; b2 = 0; b1 = 1; b0 = 0;

c_in= 0;

#100

//3+4

a3 = 0; a2 = 0; a1 = 1; a0 = 1;

b3 = 0; b2 = 1; b1 = 0; b0 = 0;

c_in = 0;

#100

//4+5

a3 = 0; a2 = 1; a1 = 0; a0 = 0;

b3 = 0; b2 = 1; b1 = 0; b0 = 1;

c_in = 0;

#100

//5+6

a3 = 0; a2 = 1; a1 = 0; a0 = 1;

b3 = 0; b2 = 1; b1 = 1; b0 = 0;

c_in = 0;

#100

//6+7

a3 = 0; a2 = 1; a1 = 1; a0 = 0;

b3 = 0; b2 = 1; b1 = 1; b0 = 1;

c_in = 0;

#100

//7+8

a3 = 0; a2 = 1; a1 = 1; a0 = 1;

b3 = 1; b2 = 0; b1 = 0; b0 = 0;

c_in = 0;

#100;

end

endmodule

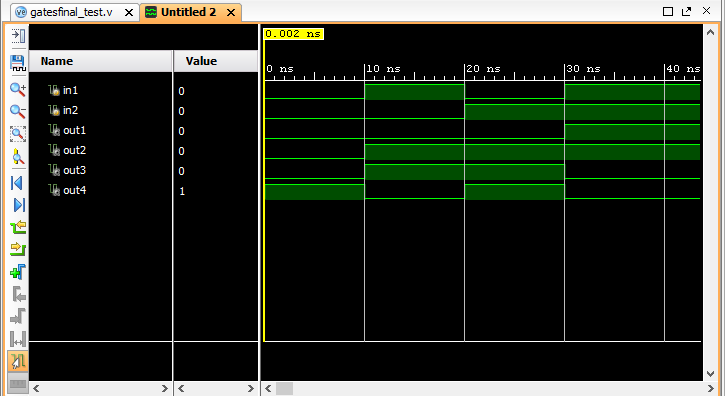

Module

module Decoder(

output out1,

output out2,

output out3,

output out4,

input in1,

input in2

);

wire in1n,in2n;

not(in1n,in1);

not(in2n,in2);

and a1(out1, in1n, in2n);

and a2(out2, in1n, in2);

and a3(out3, in1, in2n);

and a4(out4, in1, in2);

endmodule

Test Bench

module Test_Decoder;

reg in1, in2;

wire out1, out2, out3, out4;

Decoder d(out1, out2, out3, out4, in1, in2);

initial

begin

in1 = 1'b0;

in2 = 1'b0;

#10

in1 = 1'b1;

in2 = 1'b0;

#10

in1 = 1'b0;

in2 = 1'b1;

#10

in1 = 1'b1;

in2 = 1'b1;

end

endmodule

Thanks for sharing your knowledge. Keep doing good work.

ReplyDeleteGud work sitg!

ReplyDeleteAap hm sb ka bhala krtay hain allah aap ka vhala kray😁

Good Work

ReplyDelete